AUG 12 Issue 15/2010 www.edn.com

Farnell/Newark's Gary Nevison Pg 52

EDN.comment: India's \$35 tablet Pg 9

Signal Integrity Pg 21

Nano drives improve displays Pg 22

Design Ideas Pg 45

Pen puzzle pauses printer Pg 56

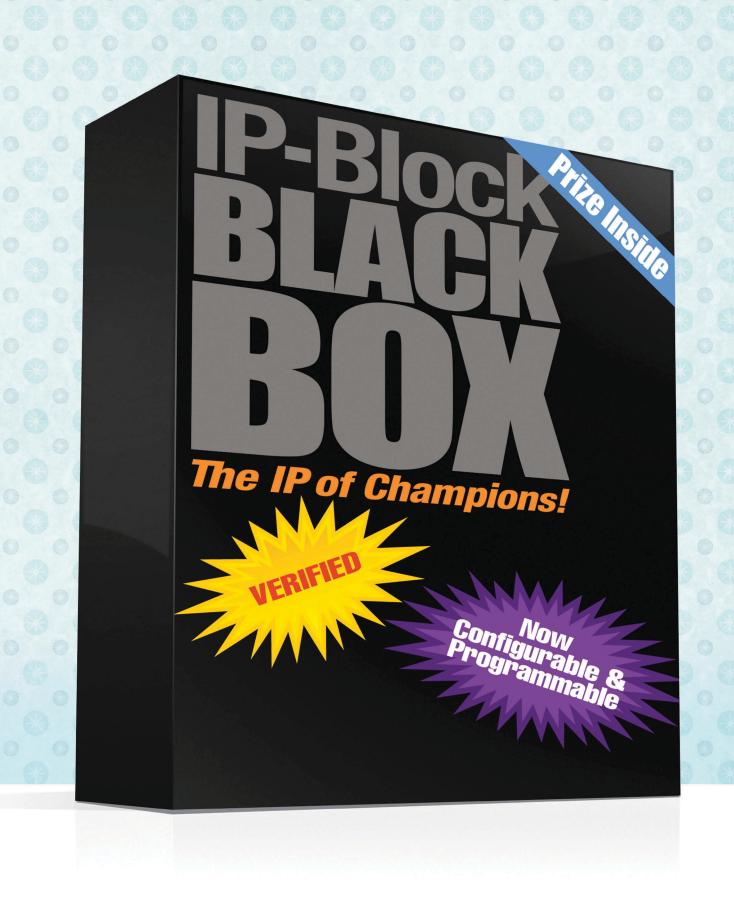

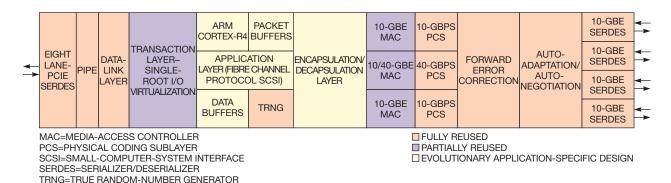

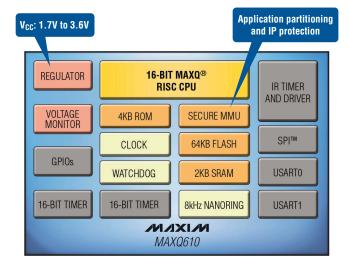

# IP INTEGRATION:

IS IT THE REAL SYSTEM-LEVEL DESIGN?

Page 34

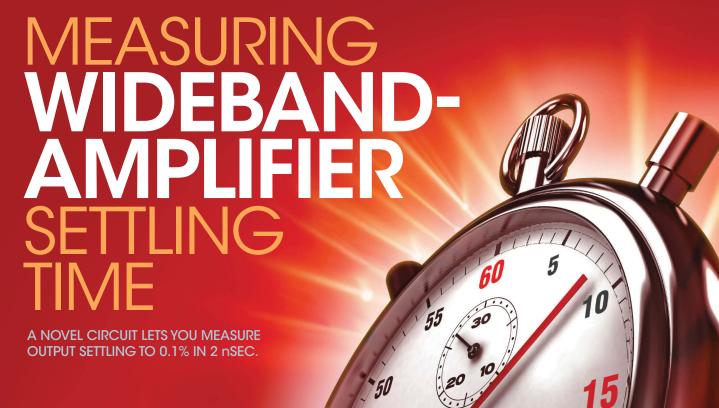

MEASURING

WIDEBANDAMPLIFIER

SETTLING TIME

Page 24

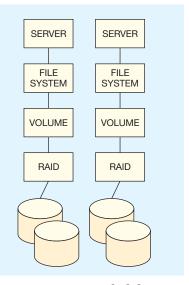

DATA STORAGE YIELDS INCREASED DESIGN PRODUCTIVITY

Page 41

## Solution: New Bergquist S-Class Gap Pad® 5000S35

Gap Pad 5000S35's natural tack makes application clean and easy to handle.

Gap Pad S-Class is perfectly suited for high performance applications such as VRMs, BGAs and ASICs.

Bergquist's newest S-Class is the perfect combination of softness, low thermal resistance and high thermal conductivity. With a low bulk

hardness (35 Shore 00) and

high thermal conductivity (5.0 W/m-K) it conforms to demanding contours while maintaining its structural integrity. It is an ideal gap filling solution for applications with fragile components that can be damaged by harder materials that cause higher mounting pressure on components. Gap Pad 5000S35 is also an excellent solution for Excellent interfacing and wet-out makes GP5000S35 ideal for fragile components with demanding contours and stack-up tolerances. nents. Gap Pad 5000S35 is also an excellent solution for

#### Ultra soft S-Class integrity offers easy application.

Gap Pad 5000S35 has a natural tack that eliminates the need for additional adhesive layers that can inhibit thermal performance. Its super soft, yet elastic nature provides excellent interfacing and wet-out, even to surfaces with high roughness or topography. Gap Pad 5000S35 features an embedded-fiberglass reinforcement that makes it puncture, shear and

> tear resistant. No tearing, flaking or crumbling – just clean and easy handling during the assembly process.

#### FREE S-Class swatch kit.

Visit our web site or call to qualify for your FREE S-Class swatch kit with product details.

FREE Gap Pad S-Class

Call 1.800.347.4572 or visit www.bergquistcompany.com/coolrun

18930 West 78th Street • Chanhassen, MN 55317 • A ISO9001:2000 registered facility (800) 347-4572 • Phone (952) 835-2322 • Fax (952) 835-0430 • www.bergquistcompany.com

# TAKE CONTROL

**From Prototype to Production!**

- 1 "Always has available product"

- 2 "Has an excellent website"

- **3 "Supports your global distribution needs"**

Digi-Key rated #1 in all categories, Source: *TechInsights*. Distributor Evaluation Study, May 2009.

- **4** "Provides on time delivery"

- 5 "Is easy to do business with"

- 6 "Most preferred distributor"

Over 465,000 electronic components in stock from more than 440 supplier partners.

The industry's broadest product selection available for immediate delivery

www.digikey.com 1.800.344.4539

\*Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2010 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

Unleash your creativity and imagine the possibilities. Then watch as they become reality with the power of Dell Precision $^{\text{\tiny M}}$  workstations and Autodesk $^{\text{\tiny B}}$  BIM software.

Dell Precision™ workstations deliver the performance and graphics needed to run demanding applications with ease. Now your team can use data-rich modeling to evaluate new design options, predict building performance and communicate more productively.

- Scalable options select systems are available with up to 192GB of memory\* and 7.5TB of internal storage

- A full range of desktop, rack and mobile workstations to fit your needs

- ISV-certified for 95 leading applications, including Autodesk®

- Stay up and running with a 3-year Limited Hardware Warranty\*\* and optional 24/7 Dell ProSupport™

Get Equipped

Find your ideal configuration online. Go to dell.com/smb/vision or call your sales rep at 1-877-952-3355

Windows® 7 Professional operating system makes the things you do every day faster and easier. With fewer clicks, faster searching, easier browsing and simpler ways to connect, there's less between you and what you want to do.

\*Actual capacity varies with preloaded material and operating environment and may be less. Significant system memory may be used to support graphics, depending on system memory size and other factors. \*\* For copy of Ltd Hardware Warranty, write Dell USA LP. Attn Warranties, One Dell Way, Round Rock, TX 78682 or visit dell.com/warranty. Remote Diagnosis is determination by online/phone technician of cause of issue, may involve customer access to inside of unit and multiple or extended sessions. If issue is covered by Limited Hardware Warranty and not resolved remotely, technician and/or part will be dispatched usually within 1 business day following completion of Remote Diagnosis. Availability varies. Other conditions apply.

# EDN 8.12.10 contents

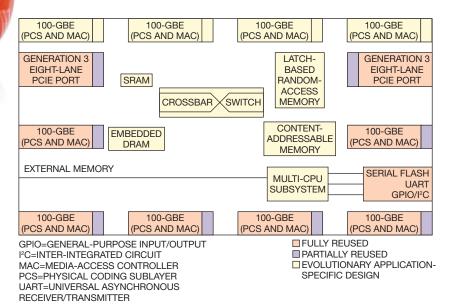

#### IP integration: Is it the real system-level design?

Increasingly, SOC design is about selecting and assembling third-party IP, not about creating new code.

By Ron Wilson, Executive Editor

#### Measuring widebandamplifier settling time

A novel circuit lets you measure output settling to 0.1% in 2 nsec.

> By Jim Williams, Linear Technology

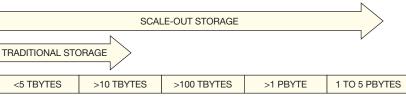

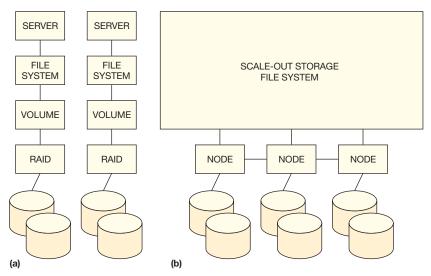

#### Data storage yields increased design productivity

→ Review how current datastorage technologies can offer an essential tool for significantly increasing the speed of design processes, enhance productivity, and avoid the unpredictability of evolving design needs.

> By Paul Rutherford, Isilon Systems

- 12 Can light beams replace electronic signals in future computers?

- 14 30-MHz generators produce predefined functions, precision pulses, and low-jitter arbitrary waves

- 14 1530-lumen, 90W light engine is incandescent-equivalent

- 16 Novellus announces product suite for advanced WLP

- 17 Virginia Tech launches smart-grid online-information portal

- 18 New light-bulb labels emphasize lumens, not watts

- 18 Cree, Philips sign licensing agreement

- 18 Online tool simplifies, speeds POL design

# DESIGNIDEAS

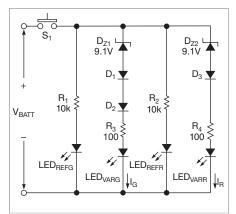

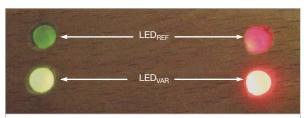

- 45 Simple battery-status indicator uses two LEDs

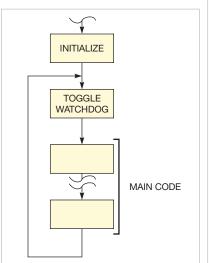

- 46 Hardware watchdog timer accepts range of frequencies

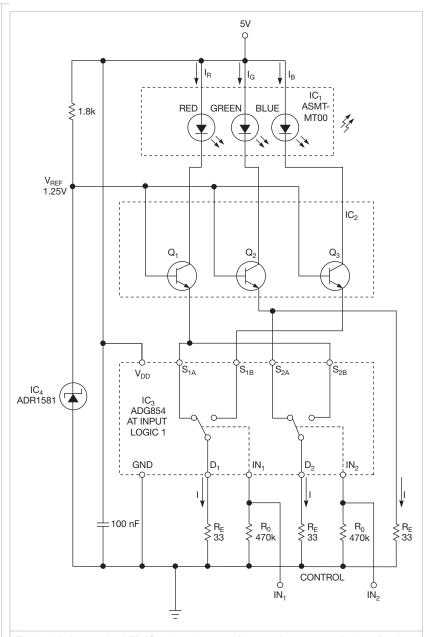

- 48 Get four colors from 2 bits

- 50 Implement trapezoidal velocity profiles in software

Yes, chip inductors are among Coilcraft's biggest sellers. But did you know we also offer a full range of other RF products like these?

They're all in stock for immediate shipment and all available as free samples for testing and evaluation.

For the full picture, visit www.coilcraft.com/RF

#### **Broadband Conical Inductors**

High impedance from 10 MHz to 40 GHz. Perfect for RF to millimeter-wave choking and bias tees. Available with leads or in surface mount versions for ruggedness and easy mounting.

#### **RFID Transponder Coils**

A variety of antenna coils for 125 kHz systems. Automotive grade models for tire pressure and keyless entry applications.

#### Air Core Inductors

For the highest possible Q and current handling, nothing beats our air core "Spring" inductors. New models offer more inductance values and smaller size.

#### **Wideband Transformers**

Our low insertion loss transformers come in a wide range of turns ratios. Use for baluns, isolation or impedance matching.

# Some people only think of us for chip inductors.

## contents 8.12.10

#### **DEPARTMENTS & COLUMNS**

- 9 EDN.comment: India's \$35 tablet: If it's possible, it could be a game changer

- 21 Signal Integrity: Water hammer

- 22 Inside Nanotechnology: Nano drives improve displays

- **Supply Chain:** ROHS recast: Electronics industry braces for further regulation

- 54 Product Roundup: Discrete Semiconductors, Switches and Relays

- 56 Tales from the Cube: Pen puzzle pauses printer

### **EDN** online contents

www.edn.com

#### ONLINE ONLY

Check out this Web-exclusive article:

Interoperable DRC/LVS language standard accelerates physical-verification turnaround time for advanced nodes

→www.edn.com/100812toca

#### **FEED YOUR NEED**

EDN's technical editors highlight notable new products, including analog and digital ICs, power components, sensors, passives, and boards. Contact the appropriate editor to submit products for consideration.

→www.edn.com/100812tocb

#### **Readers' Choice**

Here is a selection of recent articles and blog posts receiving high traffic on www.edn.com:

## DC-voltage doubler reaches 96% efficiency

→www.edn.com/100812tocc

iTunes Store woes: Apple's arrogance steadily grows

→www.edn.com/100812tocd

#### Last hope for retail set-top boxes?

→www.edn.com/100812toce

#### The time is now for 3-D stacked die

→www.edn.com/100812tocf

## Several key commodity components in "critically short supply"

→www.edn.com/100812tocg

EDN® (ISSN#0012-7515) is published semimonthly, 24 times per year, by Canon Communications LLC, 11444 W. Olympic Blvd., Los Angeles, CA 90064-1549; 310/445-4200; FAX 310/445-4299. Periodicals postage paid at Los Angeles, CA, and at additional mailing offices. SUBSCRIPTIONS—Free to qualified subscriptions: beroiters as defined on the subscription card. Rates for nonqualified subscriptions, including all issues: US, \$150 one year; \$250 two years; \$300 three years. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. For telephone inquiries regarding subscriptions, call 763/746-2792. Email: EDN@kmpsgroup.com. CHANGE OF ADDRESS—Notices should be sent promptly to PO Box 47461, Plymouth, MN 55447. Please provide old mailing label as well as new address. Allow two months for change. NOTICE—Every precaution is taken to ensure accuracy of content; however, the publisher cannot accept responsibility for the correctness of the information supplied or advertised or for any opinion expressed herein. POSTMASTER—Send address changes to EDN, PO Box 47461, Plymouth, MN 55447. Canada Post: Publications Mail Agreement 40612608. Return undeliverable Canadian addresses to Pitney Bowes Inc, PO Box 25542, London, ON NIG 682. Copyright 2010 by Canon Communications LLC. All rights reserved. Reproduction in whole or part without written permission is prohibited. Volume 55, Number 15 (Printed in USA).

# Benchmark MOSFETs

# DC-DC Buck Converter and POL Applications

|                    |    | ZP 🎤 |           |

|--------------------|----|------|-----------|

| <b>SO-8</b>        |    | 1111 |           |

| Part               | V  | nC   | $m\Omega$ |

| IRF8252PBF         | 25 | 35   | 2.7       |

| IRF8788PBF         | 30 | 44   | 2.8       |

| IRF8721PBF (Cntrl) | 30 | 8.3  | 8.5       |

| IRF7862PBF (Sync)  | 30 | 30   | 3.7       |

#### POFN (5x6

| L MI M (2VO)      |          |     |     |  |  |

|-------------------|----------|-----|-----|--|--|

| Part              | V        | nC  | mΩ  |  |  |

| IRFH7928TRPBF     | 30       | 40  | 2.8 |  |  |

| IRFH7921TRPBF (Cr | ntrl) 30 | 9.3 | 8.5 |  |  |

| IRFH7932TRPBF (Sy | nc) 30   | 34  | 3.3 |  |  |

| IRFH7934TRPBF     | 30       | 20  | 3.5 |  |  |

| IRFH7914TRPBF (Cr | ntrl) 30 | 8.3 | 8.7 |  |  |

| IRFH7936TRPBF (Sy | (nc) 30  | 17  | 4.8 |  |  |

| PQFN (3x3)    |    |     |                    |  |

|---------------|----|-----|--------------------|--|

| Part          | V  | nC  | $\mathbf{m}\Omega$ |  |

| IRFH3702TRPBF | 30 | 9.6 | 7.1                |  |

| IRFH3707TRPBF | 30 | 5.4 | 12.4               |  |

Your FIRST CHOICE for Performance

For more information call 1.800.981.8699 or visit www.irf.com

International Rectifier

THE POWER MANAGEMENT LEADER

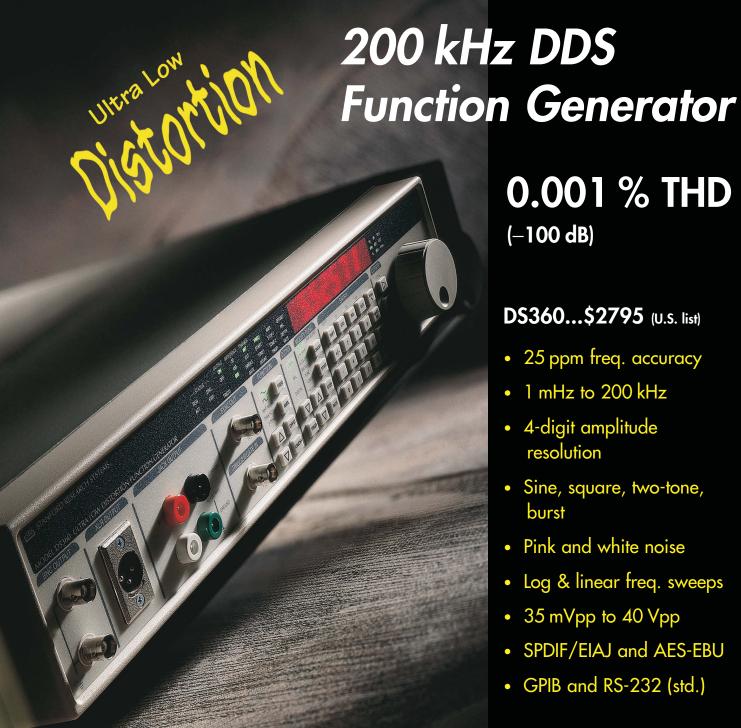

0.001 % THD (-100 dB)

DS360...\$2795 (U.S. list)

- 25 ppm freq. accuracy

- 1 mHz to 200 kHz

- 4-digit amplitude resolution

- Sine, square, two-tone, burst

- Pink and white noise

- Log & linear freq. sweeps

- 35 mVpp to 40 Vpp

- SPDIF/EIAJ and AES-EBU

- GPIB and RS-232 (std.)

The performance of a low-distortion signal source and the features of a digitally synthesized function generator are combined in a unique instrument, the DS360. With 0.001 % THD, 25 ppm frequency accuracy and functions that include sine waves, square waves, sweeps, and bursts, the DS360 delivers unparalleled precision and versatility. To make it complete we added two-tone capability (including SMPTE, DIM, CCIF), bandwidth limited white noise, SPDIF/EIAJ and AES-EBU digital outputs, and computer interfaces.

#### SUZANNE DEFFREE, MANAGING EDITOR, NEWS

## India's \$35 tablet: If it's possible, it could be a game changer

ndia is touting a \$35 "cloud"-computing-tablet prototype that includes word-processing, Web-browsing, and videoconferencing functions. If \$35 is too much for you, however, sit tight. Government officials are looking for partners to reduce the cost to approximately 10—less than I spend on coffee in a week and about the same price you would pay for a no-frills, pay-as-you-go cell phone at Target.

The move is part of a broader effort by India's government toward better education in the country and accompanies stated plans to bring broadband connectivity to the country's 25,000 colleges and 504 universities. Much like the OLPC (One Laptop Per Child) effort, which the Massachusetts Institute of Technology backs, India with its \$35 tablet aims to provide a basic, lowcost mobile-computing device that will allow the country's citizens to engage in their own education and access the Internet, ultimately allowing for a higher quality of life.

Notably, India's tablet is much less expensive than the current \$199 XO laptop from OLPC. Marvell in May announced that it had teamed with OLPC for a sleek \$100 tablet, still at a price almost three times

higher than that of India's \$35 device.

India's tablet will most likely be Linux-based, although there has been no official word on software. The prototype mockup, exhibited in late July, shows a touchscreen and storage relying on memory cards rather than hard drives. It also has an extra-cost, ac-

cording to some reports, solar-cell option, which could be the main source of power for some in rural India.

Information has not yet emerged on what components the tablet includes, what type of wireless it runs, or which manufacturer supplies the display. Details are also lacking about processor speed, battery life, compatibility, and display resolution. Promoting the device, India's MHRD (Ministry of Human Resource Development) also omitted details about how R&D will decrease the price and what companies

will manufacture the tablet. Details notwithstanding, it's safe to say the tablet's performance and debut won't be smooth as that of the iPad or any of the competing tablets from major OEMs for the established

US, European Union, and Asia-Pacific markets, but they don't need to be. Anything is better than nothing in a country where many have no computing at all. And a cloud-based system allows á la carte personalization, a good match for low-income budgets.

You have to wonder which chip

makers could afford to supply the tablet at such a low price point. Even a full \$35 BOM (bill-of-materials) cost doesn't leave much wiggle room at current component prices, at least not for all the things India's MHRD is claiming the tablet will do. But would companies such as Intel or AMD want no part of such a tablet, which could be a game changer for the Indian market? Again, the tablet aims to bring the Internet to India, taking a first step toward computing for many in the low-income country. Chip makers may find themselves offering significant discounts to even nip at the massive market opportunity, especially when you look at the projected market size.

The US Census Bureau International Data Base estimates that India will be the most populous country by 2025, surpassing China, with its population continuing to expand and projected to exceed 1.65 billion people by 2050. Electronics executives now bend over backward to land a place in the Chinese market. Imagine how they will compete when India's access to Internet devices rises.

Some wonder whether the \$35-tablet idea will fizzle out in the same way that India's previous promises for a \$20 laptop did. Even if it never moves from prototype to consumer hands, however, there's something to consider: Developing nations don't need iPads; they don't even need our netbooks, and they would not be apt to pay the accompanying price tags. They may just need simple computing that accesses the Internet through a cloud-based system.

How will the electronics supply chain provide that access, assuming it chooses to serve the needs of developing markets rather than push products that meet the needs of developed nations? The answer to that question could force a breed of designs that see the electronics industry backtracking to simpler systems, possibly cutting into chip revenue.EDN

You can reach me at suzanne.deffree@ cancom.com.

Our engineers needed a faster scope.

A scope that would display 1 million waveforms per second. So we built one.

See for yourself www.scope-of-the-art.com/ad/fasterscope

# **EDN**

#### PUBLISHER, EDN WORLDWIDE

Russell E Pratt, 1-781-869-7982; russell.pratt@cancom.com

#### ASSOCIATE PUBLISHER, EDN WORLDWIDE

Judy Hayes, 1-925-736-7617; judy.hayes@cancom.com

#### EDITOR-IN-CHIEF, EDN WORLDWIDE

Rick Nelson, 1-781-869-7970; richard.nelson@cancom.com

#### **EXECUTIVE EDITOR**

Ron Wilson

#### MANAGING EDITOR

Amy Norcross 1-781-869-7971; fax: 1-781-862-4853; amy.norcross@cancom.com Contact for contributed technical articles

#### ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@cancom.com

#### MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS

Brian Dipert, Senior Technical Editor 1-916-548-1225; brian.dipert@cancom.com

#### **NEWS**

Suzanne Deffree, Managing Editor 1-631-266-3433; suzanne.deffree@cancom.com

#### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; margery.conner@cancom.com

#### DESIGN IDEAS EDITOR

Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@cancom.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville 1-781-869-7969; fax: 1-781-862-4853; frances.granville@cancom.com

#### ASSOCIATE EDITOR

Jessica MacNeil 1-781-869-7983; jessica.macneil@cancom.com

#### **CONSULTING EDITOR**

Jim Williams, Staff Scientist, Linear Technology edn.editor@cancom.com

#### **CONTRIBUTING TECHNICAL EDITORS**

Dan Strassberg, strassbergedn@att.net Robert Cravotta, robert.cravotta@embeddedinsights.com

#### COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap Kevin C Craig, PhD, Marquette University

#### LEAD ART DIRECTOR

Marco Aguilera

#### ASSOCIATE ART DIRECTOR

Tim Burns

#### **PRODUCTION**

## Production Artists **EDN EUROPE**

Graham Prophet, Editor, Reed Publishing gprophet@reedbusiness.fr

#### **EDN ASIA**

Wai-Chun Chen, Group Publisher, Asia waichun.chen@cancom.com Kirtimaya Varma, Editor-in-Chief kirti.varma@cancom.com

#### **EDN CHINA**

#### EDN JAPAN

Katsuya Watanabe, Publisher katsuya.watanabe@cancom.com Ken Amemoto, Editor-in-Chief ken.amemoto@cancom.com

#### **EXECUTIVE OFFICERS**

Charles G. McCurdy,

Chief Executive Officer

Fred Gysi,

Chief Financial Officer

Mike Deering,

Chief Technology Officer

Ron Wall,

Senior Vice President, Publications

Kevin O'Keefe,

Senior Vice President, Events Division

Roger Burg,

Vice President, Operations

Jason Brown,

Vice President, E-media

EDN. 33 Hayden Avenue, Lexington, MA 02421. www.edn.com. Subscription inquiries: 1-763-746-2792; EDN@kmpsgroup.com. Address changes: Send notice promptly to PO Box 47461, Plymouth, MN 55447. Please provide an old mailing label as well as your new address. Allow two months for the change. Canon Communications LLC, 11444 W. Olympic Blvd., Los Angeles, CA 90064-1549; 1-310-445-4200; fax: 1-310-445-4299.

66...they make things simple. Where others find ways to complicate the process, Mill-Max consistently delivers what's needed, when it's needed, with little or no fuss. 99

At **Mill-Max** we do everything we can to make your job easier — from our easy-to-use website to quick-turnaround quotes...responsive customer service and technical support...on-time delivery... free samples...and so much more.

46 Quality is not open to compromise, and Mill-Max components meet our very stringent standards. ??

Our connectors speak for themselves...so do our customers.

To view our Design Guide, new product offerings and request a datasheet with free samples, visit www.mill-max.com/EDN608

# Can light beams replace electronic signals in future computers?

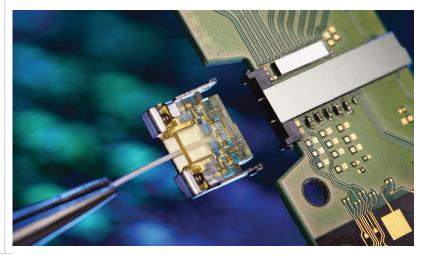

ntel has announced an advance in the quest to use light beams to replace the use of electrons to carry data in and around computers. The company has developed a research prototype employing extremely thin and light optical fibers and representing the first silicon-based optical-data connection with integrated lasers. The link can move data over longer distances and do it many times faster than today's copper technology—as fast as 50 Gbps.

Justin Rattner, chief technology officer at Intel and director of Intel Labs, demonstrated the link at the Integrated Photonics Research Conference last month in Monterey, CA. The link, according to Rattner, is akin to a "concept vehicle" that allows Intel researchers to test new ideas and continue the company's quest to develop technologies that transmit data over optical fibers, using light beams from low-cost and easy-to-make silicon instead of costly and difficult-to-make devices using exotic materials, such as gallium arsenide. Although telecommunications and other applications use lasers to transmit information, current technologies are too expensive and bulky for PC applications.

"This achievement of the ... 50-Gbps siliconphotonics link with integrated hybrid silicon lasers marks a significant achievement in our long-term vision of 'siliconizing' photonics and bringing high-bandwidth, low-cost optical communications in and around future PCs, servers, and consumer devices," Rattner says.

The prototype is the result of a multiyear silicon-photonics research agenda. It comprises a silicon transmitter and a receiver chip, each integrating all the necessary building blocks from previous Intel technologies, including the first hybrid silicon laser that Intel co-developed with the University of California—Santa Barbara in 2006 as well as high-speed optical modulators and photodetectors that Intel announced in 2007.

The transmitter chip comprises four such lasers, whose light beams each travel into an optical modulator that encodes data onto them at 12.5 Gbps. The four beams then combine and output to a single optical fiber for a total data rate of 50 Gbps. At the other end of the link, the receiver chip separates the four optical beams and directs them into photodetectors, which convert data back into electrical signals.

Intel assembles both chips using low-cost manufacturing techniques. Company researchers are working to increase the data rate by scaling the modulator speed and increase the number of lasers per chip, providing a path to future terabit-per-second optical links.

-by Rick Nelson

▶Intel Corp, www.intel.com.

#### **TALKBACK**

"Just think of the fun that you would have if the system got out into the field and then a relatively normal voltage came along and popped the fuse, and it was one of those nice soldered-in fuses, and there was no spare."—Engineer William Ketel, in EDN's Talkback section, at http://bit.ly/aDxWq0. Add your comments.

Intel's 50-Gbps silicon-photonics link allows researchers to develop and test new technologies that transmit data over optical fibers, using light beams from low-cost silicon instead of costly and hard-to-make devices using exotic materials, such as gallium arsenide.

# "I need a faster, more accurate audio analyzer."

# We knew you'd say that.

The new Agilent U8903A audio analyzer is four times more accurate and over seven times faster than its popular HP 8903B ancestor. In fact, it is among the fastest and most accurate currently in its class. It's also a more fully capable audio analyzer, letting you make crosstalk measurements and phase measurements, FFT analysis, and graph sweep. That's taking it to the next level. That's Agilent.

Learn how to migrate effortlessly - Free application note filled with tips www.agilent.com/find/AgilentU8903A

u.s. 1-800-829-4444 canada: 1-877-894-4414

## 30-MHz generators produce predefined functions, precision pulses, and low-jitter arbitrary waves

gilent Technologies has added a pair of instruments to its 33000 Series of function/ AWGs (arbitrary-waveform generators). The 33521A provides a single output channel, and the 33522A provides two channels. The gener-

ators produce sine, square, and pulse waveforms with repetition rates that you can set from 1 µHz to 30 MHz with 1-µHz resolution. square waves have nominal rise and fall times of 8.4 nsec.

The pulse waveforms have rise and fall times that you can vary independently from 8.4 nsec to 1 µsec with 100-psec or three-digit resolution. The generators can produce pulse waveforms over the full sineand square-wave repetition-rate range, whereas most competitors' units have a lower upper limit on pulse rate than they do on sine-wave frequency and square-wave repetition rate. Other built-in waveforms include positive and negative ramp, triangle, Gaussian noise with a repetition pattern that exceeds 50 years, PRBS (pseudorandom binary sequence), cardiac pulse, Gaussian pulse, exponential rise, exponential fall, haversine, Lorentz, time-dilated Lorentz, and sin(x)/x.

The new generators provide 1M-sample/channel memory depth for user-defined arbitrary tion of waveforms that are even deeper than the physical memory. The instruments' proprietary architecture also overcomes a significant shortcoming of most function-synthesizer-based generators-high waveformtiming jitter under certain conditions-for example, when a

> waveform's duration is not an exact integer multiple of the sample clock period.

The generators fully comply with the LXI (local-areanetwork extensions for instrumentation) Class C Specification.

They include USB (Universal Serial Bus) 2.0 and 10/100 BaseT Ethernet LAN ports for quick and easy connectivity to a PC or a network. A built-in Web page allows remote operation of the instruments from any Web browser. A GPIB (general-purpose-interface-bus) option allows you to connect the new generators with Agilent's 33210A, 33220A, and 33250A function/AWGs. Prices for the 33521A and 33522A start at \$1930 and \$2950, respectively.

-by Dan Strassberg **▶**Agilent Technologies, www.agilent.com/find/

33500.

For less than \$3000, the two-channel, half-rack-width 33522A delivers sine, square, and pulse waveforms to 30 MHz, plus a long list of built-in wave shapes and an unlimited number of arbitrary signals.

waveforms, and a 16M-sample/ channel memory depth is optional. The clock rate is 250M samples/sec, and the waveform definitions use 16 bits/sample, providing high time resolution, high vertical resolution, less than 0.04% total harmonic distortion, and less than 40-psecrms jitter. Waveform sequencing allows point-by-point defini-

#### 1530-LUMEN, 90W LIGHT ENGINE IS INCANDESCENT-**EQUIVALENT**

Light-engine manufacturer **OptoElectronix recently** introduced the 1530-lumen, 90W-incandescentequivalent ULE5000 LightDisc light engine. In a circular form factor, the engine works well in both ceiling fans and wall mounts. It accepts 120V ac, has an 8.1-in. diameter with an integrated heat sink, and is compatible with TRIAC (triodeac)-switch dimmers.

The LightDisc light engine sink, with high-brightness LEDs faintly visible on the white substrate ring.

The engine touts a 50,000-hour life and is available in warm- or cool-white-light ver sions. According to the company, the device is three times more efficient than incandescent or halogen devices, and it consumes only 28W of power. It also features dynamic-thermal-management-control circuitry. The LightDisc LED light engine comes with a five-year or 35,000hour warranty and sells for \$129.20 (1000) each.

-by Margery Conner OptoElectronix, www. optoelectronix.com.

#### **DILBERT By Scott Adams**

# The Power Behind the Green

High-efficiency, high-density power conversion

Call 800-735-6200 to learn more about the power of Vicor technology.

### Novellus announces product suite for advanced WLP

ovellus Systems is addressing the challenges of 3-D chip integration with the introduction of new models of the company's Vector PECVD (plasma-enhanced chemically evaporated-deposition),

system for the advanced-WLP (wafer-level-packaging)

The new PECVD, PVD, and photoresist-strip systems leverage Novellus' interconnect technology to meet the technical challenges of 3-D-integration

**WLP** technologies enable increasing I/O counts and decreasing pitch requirements, driving new metal and dielectricinterconnect applications.

connect them across short distances with cross-device copper vias, leading to significant performance gains. WLP technologies, such as microbumps, pillars, and copper RDLs (redistribution layers), enable increasing I/O counts and decreasing pitch requirements. All of these 3-D-integration schemes are driving new metal and dielectric-interconnect materials and applications.

The Sabre 3D system incorporates Novellus' Sabre Electrofill technology and includes new patented technologies that enhance void-free filling, reduce copper overburden, and improve fill uniformity at high throughputs.

You can configure Sabre 3D's modular architecture with multiple plating and pretreatment or post-treatment cells for a variety of packaging appli-

cations, including TSV, pillar, RDL, underbump metallization, and eutectic and lead-free microbumping, using materials such as copper, tin, nickel, and tin silver.

The Inova PVD system uses Novellus' patented HCM (hollow-cathode-magnetron) sputtering source with the company's lonflo technology to provide enhanced copper-sidewall coverage and low defects in highaspect-ratio TSVs. The ioninduced copper flow process enables designers to achieve void-free fill using a much thinner seed layer than competitive PVD approaches. The new Vector system uses the same patented MSSD (multistationsequential-deposition) technology that the company incorporated into previous-generation

The MSSD architecture works with the new PECVD processes to enable the system to deposit low-cost, lowtemperature films that are compatible with bonded substrates. The system also enables the deposition of high-quality dielectric liners for TSV structures in both via-middle and via-last integration schemes. The new photoresist-strip system can quickly remove 20to 100-micron-thick photoresists in the manufacture of RDLs and pillars and achieve residue-free strip and clean of high-aspect-ratio TSVs.

-by Rick Nelson Novellus.

www.novellus.com.

Vector PECVD tools.

The Sabre 3D system incorporates Novellus' Sabre Electrofill technology and includes new patented technologies that enhance void-free filling, reduce copper overburden, and improve fill uniformity at high throughputs.

Inova PVD (physical-vapordeposition), and GxT photoresist-strip systems. The company also introduced the Sabre 3D electroplating

technologies, such as TSVs (through-silicon vias) and WLP stacking schemes. TSVs allow manufacturers to vertically stack multiple chips and inter-

**RV-3029-C2 REAL TIME CLOCK MODULE** WORLD SMALLEST CERAMIC PACKAGE DIGITAL TEMPERATURE COMPENSATED RTC Accuracy: +/-3ppm @ 25C, Size: 5.0 x 3.2 x 1.2mm Voltage Range: 1.3 to 5.5V, SPI & I<sup>2</sup>C Interface sales@microcrystal.com A COMPANY OF THE SWATCH GROUP www.microcrystal.com

# Virginia Tech launches smart-grid online-information portal

irginia Polytechnic Institute and State University (Blacksburg, VA, www.vt.edu) recently announced that it has posted a beta version of its SGIC (Smart Grid Information Clearinghouse) Web portal, which will provide information on smart-grid technologies, standards, and rules and regulations.

Although the American Recovery and Reinvestment Act of 2009 (www.recovery.gov) primarily funds the smart grid, people are often unclear about its requirements, standards, and strategy. The Virginia Tech site, which will offer industry-use cases and case studies, public

awareness and education information, and work-force-training opportunities, facilitates direct sharing and dissemination of smart-grid information among various stakeholders on knowledge gained, lessons learned, and best practices.

Virginia Tech describes the SGIC as a decision-support tool for both state and federal regulators in their deliberations for rule making and evaluating the impact of their investments in smart-grid technologies and software.

The SGIC came about through a \$1.25 million, five-year contract that the US Department of Energy (www.energy.gov) awarded to the Virginia Tech ARI (Advanced Research Institute,

SGIC offers information for consumers who are just learning about the smart grid as well as industry professionals.

www.ari.vt.edu) in the National Capital Region in October 2009. Virginia Tech developed the portal with content assistance from the IEEE (www.ieee. org) and EnerNex Corp (www. enernex.com).

According to ARI Director Saifur Rahman, the Joseph R

Loring professor of engineering at Virginia Tech and principal investigator for the SGIC portal, the SGIC offers information for consumers who are just learning about the smart grid, case studies and standards for industry professionals who are implementing new technologies, and in-depth technical specifications from those who have long been developing smart-grid technology. Over the next few months, he hopes many from these groups will offer comments and suggestions so that the official portal launch will appeal to a range of people. You can submit comments on the SGIC beta site at www.sgiclearing house.ora/?a=node/1191.

—by Suzanne Deffree ▶Smart Grid Information Clearinghouse, www. sgiclearinghouse.org.

# Powerhouse.

### **AS1349 Dual Step-down Converter**

- ▶ 2 x 1.2A Output Current

- ► High Efficiency

- ► Low Current Consumption

- ► Power-down Mode

- ► Small SMD Coils

- ▶ No Schottky-Diodes

|                      | Part No.            | Input<br>Voltage | Output<br>Voltage | Output<br>Current | Efficiency | Package      |  |

|----------------------|---------------------|------------------|-------------------|-------------------|------------|--------------|--|

|                      |                     | V                | V                 |                   | %          |              |  |

|                      | Step-down Converter |                  |                   |                   |            |              |  |

|                      | AS1341              | 4.5 to 20        | 1.25 to Vin       | 0.6               | 96         | TDFN(3x3)-8  |  |

|                      | AS7620              | 3.6 to 36        | 0.6 to Vin        | 0.5               | 90         | TDFN(4x4)-12 |  |

|                      | AS1349              | 2.7 to 5.5       | 1.2 to 3.6        | 1.2               | 95         | TDFN(3x3)-12 |  |

|                      | Step-up Converter   |                  |                   |                   |            |              |  |

|                      | AS1329              | 0.65 to 5.0      | 2.5 to 5.0        | 0.315             | 95         | TS0T23-6     |  |

|                      | AS1343              | 0.9 to 3.6       | 5.5 to 42         | 0.18              | 85         | TDFN(3x3)-10 |  |

| Buck-Boost Converter |                     |                  |                   |                   |            |              |  |

|                      | AS1331              | 1.8 to 5.5       | 2.5 to 3.3        | 0.3               | 90         | TDFN(3x3)-10 |  |

|                      | AS1337              | 0.65 to 4.5      | 2.5 to 5.0        | 0.2               | 97         | TDFN(3x3)-8  |  |

Free samples online at ICdirect www.austriamicrosystems.com/ICdirect

www.austriamicrosystems.com/DC-DC

a leap ahead in analog

# New light-bulb labels emphasize lumens, not watts

he days of specifying a light bulb's output in watts will soon pass, starting in mid-2011. The FTC (Federal Trade Commission) has announced a new Lighting Facts label

Light-bulb packages will soon carry one or both of these labels, listing light output in lumens rather than watts (left). CFL packages must also have a back label, disclosing the bulbs' mercury content (right).

for incandescent bulbs, which most manufacturers are phasing out over the next five years; CFLs (compact fluorescent lights); and LED-based lights (http://ftc.gov/opa/2010/06/lightbulbs.shtm).

When incandescent bulbs dominated light-bulb technol-

ogy, describing a bulb's light output in watts made sense because the power the bulb used translated consistently to light output. The new labels may penalize higher-efficacy, lower-power-consumption CFLs and LEDs, however: A prospective buyer may think that a higher wattage rating means better light output.

The FTC requires manufacturers to place the new label on the front of lighting packages. The labels will list the bulb's brightness in lumens rather than watts. Packages for bulbs containing mercury, such as CFLs, must also include a back label indicating a Web site (www. epa.gov/cfl) that counsels consumers on the proper cleanup of broken bulbs and their safe disposal.

In addition to migrating lighting specification to a more relevant lumens, the FTC also mandates that the label must show the yearly energy cost, rather than the "yearly energy savings" that you see on many

The new labels may penalize high-efficacy, low-power CFLs and LEDs: A prospective buyer may think that a higher wattage rating means better light output.

currently selling LED lights. For example, the ecoSmart LED bulb that Home Depot sells lists energy-cost savings of as much as \$155 over its lifetime but doesn't state which technology it is comparing itself with. The new labels let consumers compare light output and yearly power costs for multiple technologies.

by Margery Conner⊳Federal Trade

**Commission**, www.ftc.gov.

# Cree, Philips sign licensing agreement

Cree and Philips recently announced a cross-licensing agreement that covers patents from both parties in the fields of blue-LED-chip technology; white LEDs and phosphors, including remote phosphors; control systems; LED luminaires and lamps; and LED backlighting of LCDs and patents in the Philips LED Luminaire Licensing Program. As Cree gets more involved in lighting end products, this agreement could be an indicator of where the companies think LEDs in luminaires are heading.

Note that these are luminaires, not the 55W replacement lamp that Philips has submitted for the US Department of Energy's L-Prize (Lighting Prize, www. lightingprize.org). The L-Prize is the first government-sponsored technology competition to spur lighting manufacturers to develop high-quality, high-efficiency solid-state lighting products to replace common

- bulbs. by Margery Conner

- **Cree**, www.cree.com.

- Philips, www.philips.com.

### Online tool simplifies, speeds POL design

**International Rectifier has** announced a free onlinedesign tool that enables electrical and thermal simulation for the company's SupIRBuck integrated POL (point-of-load) voltage regulators. The user-friendly, interactive, Web-based tool, available at http://mypower.irf. com/SupIRBuck, lets you quickly and easily select and simulate selected SupIRBuck products. Employing a designer's input and output parameters, the tool selects suitable devices for an application.

Once you enter basic requirements, the tool lets you capture schematics, create a reference design and an associated BOM (bill of materials), view waveforms, and quickly and easily perform complex thermal and application analysis to speed development time.

The tool is designed to assist a variety of designers—from power experts

International Rectifier's online-design tool enables electrical and thermal simulation for the company's SupIRBuck family of integrated POL voltage regulators.

to digital specialists with little experience in analog

design. The tool covers SupIR-Buck products with initial load currents as high as 12A, input voltages as high as 21V, and output voltages as low as 0.7V.

Support is available from customizable demo kits, reference designs, data sheets, and application notes. All of these materials are available at the company's Web site.

by Paul RakoInternational Rectifier,

International Rectifier, www.irf.com.

# DESIGN NOTES

### 2-Phase, Dual Output Synchronous Boost Converter Solves Thermal Problems in Harsh Environments – Design Note 481

Goran Perica

#### Introduction

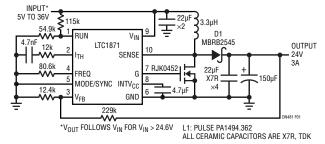

Boost converters are regularly used in automotive and industrial applications to produce higher output voltages from lower input voltages. A simple boost converter using a Schottky boost diode (Figure 1) is often sufficient for low current applications. However, in high current or space-constrained applications, the power dissipated by the boost diode can be a problem especially in high ambient temperature environments. Heat sinks and fans may be needed to keep the circuit cool, resulting in high cost and complexity.

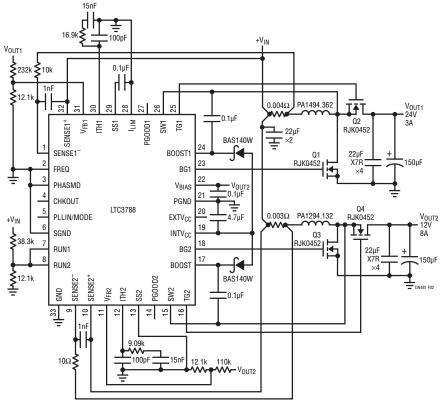

To solve this problem, the Schottky output rectifier can be replaced by a synchronous MOSFET rectifier (Figure 2). If MOSFETs with very low  $R_{DS(ON)}$  are used, the power dissipation can be reduced to the point where no heat sinks or active cooling is required, thus reducing costs and saving space.

#### **Advantages of Synchronous Rectification**

Consider the power dissipation of the single output circuit in Figure 1. The output diode D1 carries 6.7A of RMS current to produce 3A of output current from a 5V input. At this current level, diode D1's voltage drop is 0.57V, resulting in 1.6W of power lost as heat. Dissipating 1.6W in an 85°C (or higher) automotive operating environment is not trivial. To keep the circuit cool, heat sinks, cooling fans and multilayer printed circuit boards must be used. This, of course, adds complexity, cost and size to an ostensibly simple boost converter.

Figure 1. Although This Simple Circuit is Capable of 3A of Output Current, Beware of Power Dissipation in the Output Diode D1

A far better solution (featured in a dual output configuration) is shown in Figure 2, where a synchronous power MOSFET rectifier replaces the output diode. Under the same conditions, the voltage drop across output synchronous MOSFET Q2 is only 42mV or 7.4% of the voltage drop in the diode D1. The resulting power dissipation of 115mW in Q2 is relatively trivial. Another advantage of using a MOSFET as the output rectifier is the elimination of leakage current, about 10mA in the case of the MBR2545 diode—an additional 240mW of power dissipation in the application of Figure 1.

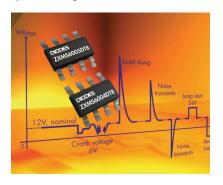

#### **Dual Output Automotive Boost Converter**

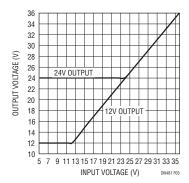

Figure 2 illustrates a typical automotive boost application with a 5V to 36V input voltage range. Here, the converter produces a 12V output for generic automotive loads such as entertainment systems, and a 24V output for circuits such as high power audio amplifiers. The two outputs are completely independent and can be controlled separately.

Because the circuit in Figure 2 is a boost converter, the output voltage can be regulated only for input voltages that are lower than the output voltage. The output voltage regulation versus input voltage is shown in Figure 3. When the input voltage is higher than the preset output voltage, synchronous MOSFETs Q2 and Q4 are turned continuously ON and boost MOSFETs are not switching. This feature allows the converter to be used in applications that require boosting only during load transients such as cold-cranking of a car engine. In this case, the LTC®3788 circuit's input voltage could be as low as 2.5V.

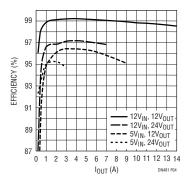

The efficiency of this converter (Figure 4) is high enough that it can be built entirely with surface mount components, requiring no heat sinks. A multilayer PCB with large copper area may be sufficient to dissipate the small amount of heat resulting from the MOSFETs' DC resistance, even at high ambient temperatures.

CT, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

Figure 2. The LTC3788 Converter is Over 95% Efficient Even Under Worst-Case Conditions. When V<sub>IN</sub> > V<sub>OUT(SFT)</sub>, Efficiency Approaches 100% as Shown in Figure 4

Figure 3. The Output Voltage Follows the Input Voltage when  $V_{IN} > V_{OUT(SET)}$

If higher output currents are required, or if lower output ripple voltage is desired, the two LTC3788 channels can be combined for a single current-shared output. Simply connect the two outputs and short the respective FB, ITH, SS and RUN pins. Because the two channels operate out of phase, output ripple currents are greatly reduced—nearly canceling out at 50% duty cycle. Thus, smaller output capacitors can be used with lower output ripple currents and voltages.

www.linear.com

Figure 4. The Converter in Figure 2 Peaks at 95% Efficiency when Operating from a 5V Input

#### Conclusion

The LTC3788 dual synchronous boost controller is a versatile and efficient solution for demanding automotive and industrial applications. By minimizing power losses in the output rectifier, this converter can be designed in a very small footprint and operate safely at elevated ambient temperatures.

For applications help, call (408) 432-1900, Ext. 3788

#### BY HOWARD JOHNSON, PhD

### Water hammer

or the second time in as many years, in the dead of night, a water buffalo lumbered into the village square and promptly fell into the community well. Ernie, the village engineer, argued that the citizens of the village should stop using the well and instead install a system of water pipes from the artesian spring on the mountainside behind the village.

He embellished his plan with a motor timer, a large electric snap-action water valve, and a flow regulator. The system would, he said, provide a reasonable, continuous flow of clean, potable water during the daytime. The excess flow could irrigate a system of flower beds, replacing those that the water buffalo's

cial progress. He felt needed. The villagers built him a hut when he arrived. Here, he could forget all the unpleasantness of his last assignment.

When he returned from the city, Ernie labored for weeks burying 2500 feet of 4-in. steel irrigation pipe leading from the spring to the village far below.

brief but deadly rampage had destroyed. At night, the valve would shut, removing from the central village square the nuisance of fresh water available to the local livestock.

The villagers approved. They raised a fund and launched Ernie on a journey to the nearest city to procure the necessary supplies. Ernie felt lucky to have this position. Tucked away high in the mountains of Bhutan, he could devote his engineering skill to the cause of so-

He installed the valve and controller at the receiving end of the pipe. When the electric valve finally snapped open, water immediately gushed from the pipe at a rate of 30 gallons per minute, just as he had planned.

The villagers shouted and tossed their hats in the air. They plugged the old well with sand. They threw a feast. Later that night, as Ernie sat basking in the glow of his recent success, he heard the electric valve click shut. The pipe exploded, and an unstoppable mass of water, the whole unregulated flow of a 4-in. pipe, flooded the village.

Ernie failed to take into account the momentum of the enormous column of water moving inexorably toward the village; 2500 feet of 4-in. pipe holds

Currents flowing in a long wire possess inductance, a property much like the momentum of flowing water.

about 13,000 lbs of water. That much water does not just suddenly stop moving because someone closed a snap-action valve.

You must slowly shut down these types of systems—over a much longer time than the round-trip delay of pressure waves traveling end to end throughout the system. At a propagation velocity of almost 5000 feet/sec, the round-trip propagation delay of pressure waves traveling there and back through Ernie's column of water is about 1 second. Slowly closing the valve over a period of, say, 10 seconds would reduce by a factor of 10 the peak amount of pressure needed to stop the movement of all that water.

Electrical circuits obey a similar principle. Currents flowing in a long wire possess inductance, a property much like the momentum of flowing water. Suddenly arrest the flow of current at the end of a long wire, and you will see a brief but intense inductive-voltage spike. If the spike is sufficiently large, it can destroy your circuit just as easily as Ernie's plumbing blew up his chance at a successful second career. EDN

Howard Johnson, PhD, of Signal Consulting, frequently conducts technical workshops for digital engineers at Oxford University and other sites worldwide. Visit his Web site at www.sigcon.com, or e-mail him at howie03@sigcon.com.

#### INSIDE NANOTECHNOLOGY

#### BY PALLAB CHATTERJEE, CONTRIBUTING TECHNICAL EDITOR

## Nano drives improve displays

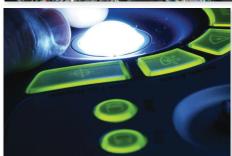

isplay technology is currently realizing the benefits of nanotechnology in lighting support for the displays and the display construction itself. One of the new display technologies is the Mirasol display (www.mirasoldisplays.com) from Qualcomm (www.qualcomm.com). This MEMS (microelectromechanical-system)-on-glass device targets low-power, daylight-readable color displays for portable-system applications.

Most LCD devices operating at low power, such as with mobile phones and tablet PCs, have issues with color representation. In varying light, the color accuracy of the display changes, altering the viewer's perception of the image. The Mirasol display attempts to overcome these issues.

The display is a front-reflective display rather than a traditional backlit display. The properties of nanoscale materials combine with advanced MEMS-processing techniques, allowing the display to mimic naturally occurring phenomena. The display works by creating a color from an interference pattern on the reflected light that hits the top of the display. This process is the same one that makes a butterfly's wing shimmer and display different colors.

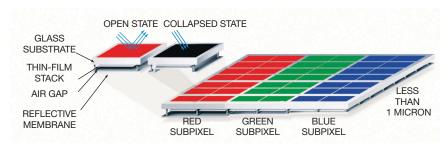

The display uses red, green, and blue subpixels to create a single pixel measuring less than 1 micron. Each of the colored subpixels comprises cells, which form an array of devices. An applied voltage then switches these devices to "collapse" the MEMS device and turn off the reflective element (Figure 1).

The Mirasol display is just one example of the use of nanotechnology in a diverse range of applications. The area of nanomaterials—compounds, elements, and polymers that behave differently or exhibit new and unique properties at the nanoscale—is bringing many new support applications to electronics.

In the case of products from Cima NanoTech (www.cimananotech.com), the key nanomaterial is nanocrystalline silver. With its high conductive characteristics, silver has been in use as a standard material for more than 100 years. Cima formulates the silver and silver/ copper into nanoparticle form and places these particles in suspensions and emulsions that designers can apply to various surfaces. Using self-assembly techniques, these nanoparticles form microscopic conductive networks that are transparent but that have properties similar to those of traditional opaque materials. Designers can apply the nanoparticle layer as a transparent film with an inexpensive, wet-rolling process in a large format, so it can become a low-cost, effective EMI (electromagnetic-interference) filter for plasma and other large displays. Designers can also pattern the material to form large-format resistive-touch-sensor overlays for LCD screens. In a new and growing application, the silver-and-copper particle solution can find use in conductive inks. Designers are able to print these inks on a surface using time-proven ink-jet technology.

This ability to print a conductor is drastically changing the RF- and PCB (printed-circuit-board)-prototyping flows by allowing, for example, the creation of one-time unique antenna designs that designers print and test on paper. Designers can similarly print a few fine-pitch prototypes on paper or mylar to test a design. The technique currently works in single-layer-system applications. However, multilayer-system applications are in progress.

Quantum dots are nanoparticles that have tunable optical characteristics. Companies including Nanosys (www. nanosysinc.com) and Zymera (www. zymera.com) have turned these properties into commercial products. Nanosys has a series of quantum-dot lighting techniques that color-correct the wavelength of backlit LEDs in cell phones. Zymera is using the dots as bioluminescent particle tags for drugs to track the absorption and location of certain medications in the treatment of cancer, for example.EDN

Figure 1 The Mirasol display uses MEMS on glass to create colors using interference patterns. The red subpixel has an open state and a collapsed state. The red-, green-, and blue-pixel design using MEMS receives light modulation from applied voltage, color selection from constructive interference, and memory from electromechanical behavior.

Contact me at pallabc@siliconmap.net.

# The Trade Shows that Connect You with the Electronics Manufacturing Industry

September 28–30, 2010

Donald E. Stephens Convention Center

Rosemont (Chicago), IL

ElectronicsMidwest.com

February 8–10, 2011 Anaheim Convention Center Anaheim, CA ElectronicsWestShow.com

**April 6–7, 2011**Boston Convention & Exhibition Center Boston, MA

Electronics-NE.com

Find the suppliers, tools, and services you need to make your product, process, and business more efficient, cost-effective, and profitable.

5512\_AS\_EL10

For information on attending or exhibiting, please call 310/445-4200 or visit CanonTradeShows.com

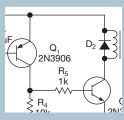

ou use wideband amplifiers in instrumentation, waveform-synthesis, data-acquisition, and feedback-control systems. To ensure a robust design for these systems, you must verify precision operation at high speeds. This requirement presents a difficult measurement challenge. Wideband operational amplifiers feature dc precision of 0.2-mV offset voltage with gain-bandwidth products of 400 MHz

and slew rates of 2500V/µsec (Reference 1). IC designers face a trade-off between fast slew rates and short ring times. Fast-slewing amplifiers generally have extended ring times. This combination complicates your amplifier choice and the frequency compensation you use (see sidebar "Practical considerations for amplifier compensation"). Additionally, the architecture of very fast amplifiers usually dictates trade-offs, which degrade dc-error terms.

#### **SETTLING TIME DEFINED**

It is relatively easy for you to verify amplifier dc specifications. Literature defines the measurement techniques you use. You need to use more sophisticated approaches to produce reliable ac specifications. Measuring anything at any speed requires care. Dynamic measurements are particularly challenging, and amplifier settling time is difficult to determine (references 2 through 7).

Settling time is the elapsed time from an input application until the output arrives at and remains within a specified error band around the final value. Amplifier manufacturers usually specify it over a full-scale transition.

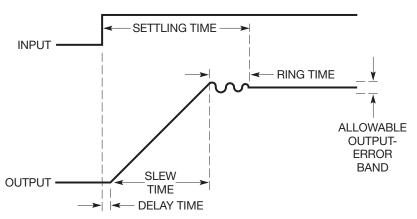

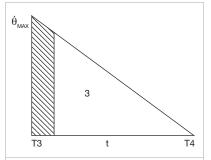

Settling time has three distinct components (Figure 1). The delay time is small and almost entirely due to the amplifier's propagation delay. No output movement occurs during this in-

terval. During slew time, the amplifier moves at its highest speed toward the final value. Ring time defines the region during which the amplifier recovers from slewing and ceases movement within some defined error band. Measuring settling times of nanoseconds requires a careful approach and experimental technique.

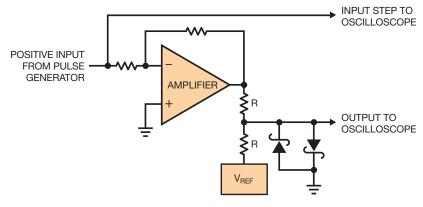

The traditional way for measuring settling time is with a circuit that uses the false-sum-node technique (Figure 2). The resistors and amplifier form a bridge network. The amplifier output steps to the input voltage when you drive the input, assuming that the circuit is using ideal resistors. During the slew period, the diodes bound the settle node, limiting the voltage excursion. When settling occurs, the oscilloscope's probe voltage should be 0V. The resistor divider's attenuation causes the probe's output to be one-half of the settled voltage.

In theory, this circuit should allow you to observe fast settling to small amplitudes. In practice, you cannot rely on it to produce useful measurements. The circuit has several flaws, including a requirement for the input pulse to have a flat top within the required measurement limits. Typically, you are interested in settling of less than 5 mV for a 5V step. No general-purpose pulse generator holds the output amplitude and noise within these limits. You cannot distinguish between generator-caused aberrations and amplifier-related ones.

The oscilloscope connection also presents problems. As probe capacitance rises, the ac loading of the resistor junction influences the observed

#### AT A GLANCE

- It is difficult to measure the settling time of fast amplifiers.

- One method of measurement is to use an old analog sampling oscilloscope.

- This circuit uses a currentsteering bridge and an analog multiplier IC.

- The two methods correlate well.

- The measurement limits are 2 mV and 2 nsec.

settling waveforms. The excessive input capacitance of 1× probes makes them unsuitable for this measurement. A 10x probe's attenuation sacrifices oscilloscope gain, yet its 10-pF input capacitance still introduces a significant lag at nanosecond speeds. If you use an active 1x, 1-pF FET (field-effect-transistor) probe, it largely alleviates this problem, but a more serious issue remains.

You use clamp diodes at the settle node to reduce the voltage swing during amplifier slewing. This approach is intended to prevent the circuit from overdriving the oscilloscope input. Unfortunately, the 400-mV drop across the Schottky diodes means that the oscilloscope will undergo an unacceptable overload (Reference 8). Oscilloscopes' overdrive-recovery characteristics vary widely among models and brands, and manufacturers typically do not specify it. At 0.1% resolution, the oscilloscope typically undergoes a 10-times overdrive at 10 mV/division, making the desired 2.5-mV baseline unattainable.

Figure 1 The components of settling time include delay, slew, and ring times. Using fast amplifiers reduces slew time, although longer ring time usually results.

#### Pulse Transformers

10 Nanoseconds to 100 Microseconds, ET Rating to 150 Volt Microsecond, Manufactured and tested to MIL-PRF-21038.

#### Multiplex Data Bus Pulse Transformers

Plua-In units meet the requirements of QPL-MIL-PRF 21038/27. Surface units are electrical equivilents of QPL-MIL-PRF 21038/27.

#### DC-DC Converter Transformers Input voltages of 5V, 12V, 24V And 48V.

Standard Output Voltages to 300V (Special voltages can be supplied). Can be used as self saturating or linear switching applications. All units manufactured and tested to MIL-PRF-27.

## 400Hz/800Hz

0.4 Watts to 150 Watts. Secondary Voltages 5V to 300V. Units manufactured to MIL-PRF-27 Grade 5, Class S (Class V, 155°C available).

Call toll free 800-431-1064

in NY call 914-738-1400 Fax 914-738-8225 Electronics,Inc.

143 Sparks Ave. Pelham, N.Y. 10803 Mail: info@picoelectronics.com www.picoelectronics.com

Figure 2 A popular summing scheme for settling-time measurement provides misleading results with fast amplifiers.

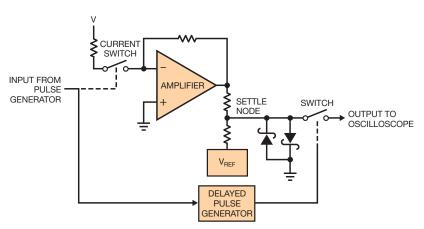

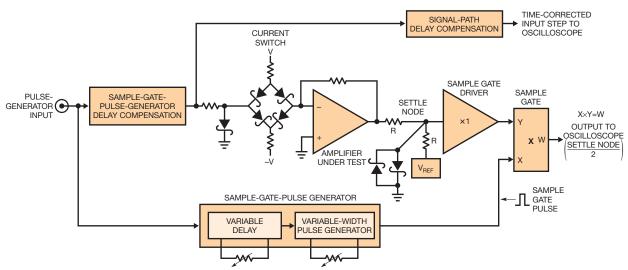

Figure 3 The proposed circuit's conceptual arrangement is insensitive to pulse-generator aberrations and eliminates oscilloscope overdrive. The input switch gates a current step to the amplifier under test. A delayed-pulse generator controls a second switch, which prevents the oscilloscope from monitoring the settle node until settling is nearly complete.

With this arrangement, the measurement becomes hopeless at nanosecond speeds.

Thus, your measuring wideband amplifier settling time requires an oscilloscope that is somehow immune to overdrive as well as a flat-top pulse generator. The only oscilloscope technology that offers inherent overdrive immunity is the classic analog sampling oscilloscope. Do not confuse these scopes with modern digital sampling oscilloscopes that have overdrive restrictions (Reference 8). Several documents explain the operation of classic sampling oscilloscopes (references 9 through 13). Although you can buy these instruments used, their manufacturers no longer make them. You can, however, construct a circuit that borrows the overload advantages of classic analogsampling-oscilloscope technology. You can also endow the circuit with features for measuring nanosecond settling times.

You can avoid the flat-top-pulse-generator requirement by switching current rather than voltage. It is easier to gate a quickly settling current into the amplifier's summing node than to control a voltage. This approach eases the input pulse generator's job, although it still must have a rise time of approximately 1 nsec to avoid measurement errors.

#### PRACTICAL MEASUREMENT

A circuit that can measure widebandamplifier settling time shares attributes

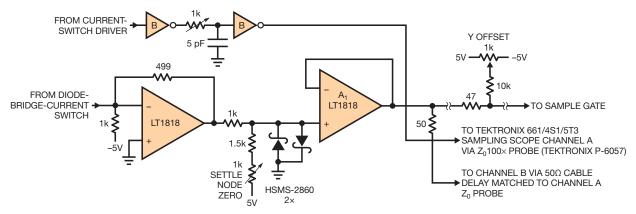

Figure 4 The diode bridge cleanly switches input current to the amplifier. A multiplier-based sampling switch eliminates the signal's presettling excursion. You compensate the input-step time reference and sample-gate-pulse generator for any circuit delays.

with the classic method, although some new features appear (Figure 3). The oscilloscope connects to the settle point by a switch. You determine the switch's state by triggering a delaying pulse generator from the input pulse. You arrange the delayed pulse generator's timing so that the switch does not close until settling is nearly complete. In this way, you sample the incoming waveform in both time and amplitude. No off-screen activity occurs on the oscilloscope; hence, you never subject the oscilloscope to overdrive.

You control the switch at the amplifier's summing junction with the input pulse. This switch gates current to the amplifier through a voltage-driven resistor. This approach eliminates the requirement for a flat-top pulse generator,

# THE SAMPLE-GATE MULTIPLIER IC MUST PASS WIDEBANDSIGNAL-PATH INFORMATION WITHOUT INTRODUCING ALIEN COMPONENTS.

although the switch must be fast and devoid of drive artifacts.

For more detail, you split the delayed pulse generator into a delay block and a pulse generator, which you can vary independently (Figure 4). The input step to the oscilloscope runs through a section that compensates for the propagation delay of the settling time's measurement path. Similarly, another delay compensates the sample gate's pulsegenerator propagation delay. This delay causes a phase-advanced version of the pulse that triggers the amplifier under test to drive the sample gate's pulse generator. This approach improves minimum measurable settling time by making irrelevant the sample gate's pulse-generator propagation delay.

The most striking new aspects of Figure 4's circuit are the diode bridge switch and the multiplier IC. The diode bridge's balance combines with matched, low-capacitance Schottky diodes and high-speed drive to yield clean switching. The bridge quickly switches

current into the amplifier's summing point, with settling time within 1 nsec. The diode clamp to ground prevents excessive bridge-drive swings and ensures that nonideal input-pulse characteristics are nearly irrelevant.

The sample-gate multiplier IC has stringent requirements. It must faithfully pass wideband-signal-path information without introducing alien components, particularly those deriving from the switch-command channel that provides the sample-gate pulse. Conventional choices for the sample-gate switch would include FETs or a sampling diode bridge. But FETs' parasitic gate-to-channel capacitances would result in large gate-drive-originated feedthrough into the signal path. For almost all FETs, this feedthrough is many times larger than the signal you are observing and would induce oscilloscope overload and obviate the switch's purpose. The diode bridge is better; its small parasitic capacitances tend to cancel, and its symmetrical, differential structure results in low feedthrough. Practically, however, the bridge requires dc and ac trims and complex drive and support circuitry (references 3, 4, 7, and 14).

To avoid these problems, the sample-gate multiplier IC functions as a wideband high-resolution switch with low feedthrough. The great advantage of this approach is that you can maintain the switch-control channel inband. You hold the transition rate within the multiplier IC's 250-MHz bandpass. The multiplier's wide bandwidth means that you always control the switch command's transition. There are no out-of-band responses, greatly reducing feedthrough and parasitic artifacts.

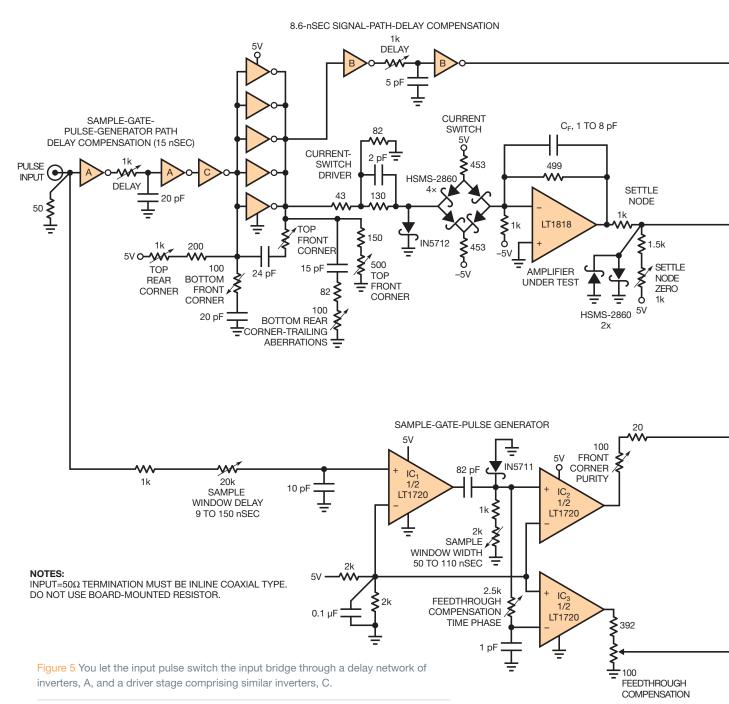

#### **SETTLING-TIME CIRCUITRY**

You let the input pulse switch the input bridge through a delay network of inverters, A, and a driver stage comprising similar inverters, C (Figure 5). The delay compensates the sample-gate pulse generator's delayed response. This step ensures that the sample gate's pulse can occur immediately after the end of the amplifier under test's slew time. You choose the delay range so that the sample-gate pulse can occur before the amplifier slews. This capability is unused in normal operation, although it guarantees that you will always be able to

capture the settling interval.

The C inverters form a noninverting driver stage you use to switch the diode bridge. You adjust various trims to optimize the driver output pulse shape (see sidebar "Settling-time circuit-trimming procedures" with the Web version of this article at www.edn.com/100812df). This approach provides a clean, fast impulse to the diode bridge. This highfidelity pulse is devoid of undamped components. It prevents radiation and

THE PULSE IS DEVOID OF UNDAMPED COM-PONENTS AND PRE-**VENTS RADIATION** FROM DEGRADING THE MEASUREMENT NOISE FLOOR.

disruptive ground currents from degrading the measurement noise floor. The driver also activates the B inverters, which supply a time-corrected input step to the oscilloscope.

The driver's output pulse transitions through the 1N5712 diode clamp's forward-voltage potential in less than 1 nsec. This transition causes an essentially instantaneous switching of the diode bridge. The cleanly settling current into the amplifier under test's sum-

ming point causes a proportionate amplifier output movement. You set up a negative bias current at the amplifier's summing point with a 1-k $\Omega$  resistor pulled to -5V. That current combines with the input current step to produce a -2.5 to +2.5V amplifier output transition. You feed this amplifier's output to a voltage divider biased to 5V. You adjust the potentiometer to a nominal 500 $\Omega$  so that when the amplifier under test transitions to -2.5V, the node clamped by the two Schottky diodes

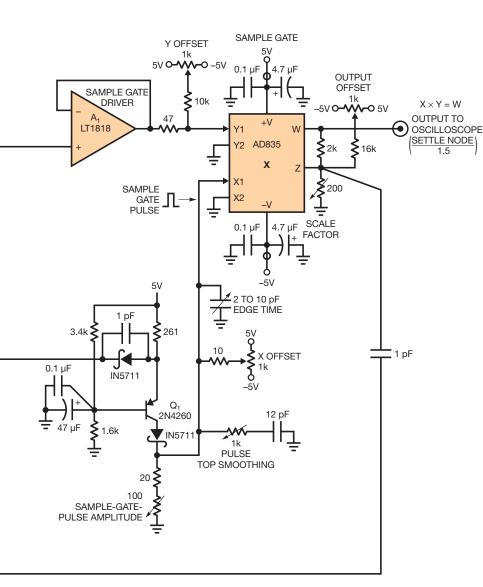

transitions to 0V. Buffer amplifier  $A_1$  unloads this clamped settle node and provides the settling-time signal to the AD835 multiplier IC.

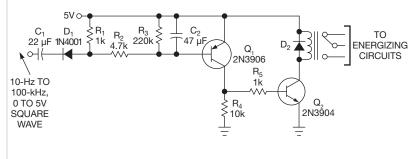

The other signal path to the multiplier IC uses a  $20\text{-}k\Omega$  potentiometer to set a delay time of the input pulse. This potentiometer feeds three comparators, and you use a  $2\text{-}k\Omega$  potentiometer to set the delayed pulse width. This step sets the sample gate's on-time. The  $Q_1$  stage forms the sample gate's pulse into a clean, fast rise time. This technique

furnishes pure, calibrated-amplitude, on/off switching instructions to the sample gate's multiplier IC. Appropriate setting of the sample gate's pulse delay means that the oscilloscope will not see any input until settling is nearly complete, eliminating oscilloscope overdrive. You adjust the sample window's pulse width so that you can observe all the remaining settling activity. In this way, the oscilloscope's output is reliable, and you can take meaningful data.

# TIME-CORRECTED INPUT STEP TO OSCILLOSCOPE

#### **PERFORMANCE RESULTS**

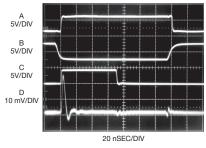

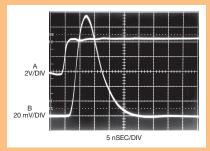

The circuit performs admirably (Figure 6). Trace A is the time-corrected input pulse, Trace B is the amplifier's output, Trace C is the sample gate's pulse, and Trace D is the settling-time output. When you interpret the waveform placement, note that Trace B appears time-skewed relative to time-corrected Trace A. This skew accounts for Trace B's false movement before Trace

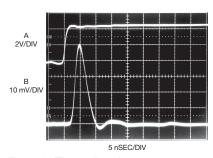

Figure 6 The settling-time circuit's waveforms include the time-corrected input pulse (Trace A), amplifier under test's output (Trace B), sample gate's trace (Trace C), and settling-time output (Trace D). You can vary the sample-gate window's delay and width. Trace B appears time-skewed relative to the time-corrected Trace A.

Figure 7 By expanding the vertical and horizontal scales, you can see the 9-nsec amplifier settling to within 5 mV (Trace B). Trace A is the time-corrected input step.

A's ascent. When the sample gate's pulse goes high, the sample gate switches cleanly. You can easily observe the last 20 mV of the amplifier's slewing. You can also see the entire ring time and the amplifier settling nicely to a final value.

When the sample gate's pulse goes low, the sample gate switches off with only 2 mV of feedthrough. No off-screen activity occurs at any time, and you never subject the oscilloscope to overdrive.

You can adjust the vertical and hori-

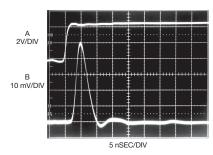

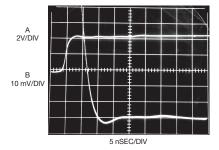

zontal scales of the oscilloscope to make the settling details more visible (**Figure** 7). You measure settling time from the onset of the time-corrected input pulse. Additionally, you calibrate the settling signal's amplitude with respect to the

#### PRACTICAL CONSIDERATIONS FOR AMPLIFIER COMPENSATION

There are a number of practical considerations when you compensate the amplifier to get the fastest settling time (see Figure 1 in the main text). Once you choose an amplifier, the only settling variable you can change is the ring time by changing the amplifier's compensation network. Because slew time is usually the dominant lag, it is tempting to select the fastest-slewing amplifier available. Unfortunately, fast-slewing amplifiers usually have extended ring times, which negate their speed advantage. If you damp out the ringing with large compensation capacitors, it results in protracted settling times.

The key to good settling times is to choose an amplifier with the right balance of slew rate and recovery characteristics and then properly compensate it. This is harder than it sounds because you can't predict amplifier settling time or extrapolate it from any combination of data-sheet specifications. You must measure settling time in the intended configuration.

A number of terms combine to influence settling time. They include amplifier slew rate and ac dynamics, layout capacitance, source resistance and capacitance, and the compensation capacitor. These terms interact in a complex manner, making predictions hazardous. Spice aficionados should take notice. If you replace the parasitic components with a purely resistive source, you still can't readily predict amplifier settling time. The parasitic-impedance terms make a difficult problem messier.

The only way to deal with the parasitic terms is to adjust the feedback compensation capacitor,  $\mathbf{C}_{\mathrm{F}}$ . When you properly adjust the value of  $\mathbf{C}_{\mathrm{F}}$ , it rolls off the amplifier's gain

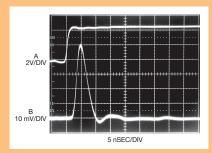

at the frequency that permits the best dynamic response. You achieve the best settling results when you select the capacitor to functionally compensate for all the terms (Figure A).

Trace A is the time-corrected input pulse, and Trace B is the amplifier's settle signal. The amplifier comes cleanly out of slew and settles to 5 mV in 9 nsec. The sample gate opens just after the second vertical division. The waveform signature is

Figure A Optimizing the compensation capacitor permits a tight waveform signature, a nearly critically damped response, and a 9-nsec settling time. Trace A is the time-corrected input step. Trace B is the settle signal.

Figure C This severely underdamped response is due to the lack of a feedback capacitor. Note the five-times vertical-scale change versus that of Figure A. Settling time is 33 nsec.

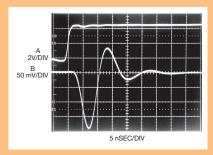

tight and nearly critically damped. When you use too large a feedback capacitor the settling is smooth, although overdamped (Figure B), giving you a 13-nsec penalty that results in a 22-nsec settling time. Eliminating the feedback capacitor results in a severely underdamped response with resultant excessive ring-time excursions (Figure C). Settling time goes out to 33 nsec. Using a feedback capacitor that is too small results in an underdamped response requiring

Figure B This overdamped response ensures freedom from ringing, even with component variations in production. The penalty is a 22-nsec settling time. Note the two-times vertical-scale change versus that of Figure A.

Figure D An underdamped response results from an undersized capacitor. Component-tolerance budgeting prevents this behavior. Note the five-times vertical-scale change versus that of Figure A. Settling time is 27 nsec.

amplifier, not the settle node. This approach eliminates ambiguity due to the settle node's resistor ratio. Trace A is the time-corrected input pulse, and Trace B is the settling output. You can easily observe the last 50 mV of slew.

27 nsec to settle (Figure D). Note that figures B, C, and D require you to reduce the vertical scale to capture the nonoptimal responses.

When you trim the feedback capacitor for optimal response. the source, stray, amplifier, and compensation-capacitor tolerances are irrelevant. If you don't use individual trimming, you must consider these tolerances to determine the feedback capacitor's production value. Stray and source capacitance and output loading, as well as the feedback capacitor's value, affect ring time. The relationship is nonlinear, although some guidelines are possible. The stray and source terms can vary by  $\pm 10\%$ , and the feedback capacitor is typically a ±5% component. These figures assume a resistive source. If the source has substantial parasitic capacitance, such as a photodiode or a DAC, this number can easily reach ±50%. Additionally, amplifier slew rate has a significant tolerance, which the data sheet states. To obtain a productionfeedback-capacitor value, you determine the optimum value by individual trimming with the production-board layout. Remember that board-layout parasitic capacitance counts too. Then, factor in the worst-case percentage values for strav- and source-impedance terms, slew rate, and feedback-capacitor tolerance. Add this information to the trimmed capacitors' measured value to obtain the production value. This budgeting is perhaps unduly pessimistic. The errors should sum in an rms (root-mean-square) fashion, not a purely additive way.

The amplifier settles within 5 mV, or 0.1%, in 9 nsec after you optimize the amplifier under test's feedback capacitor, C<sub>r</sub>, (see sidebar "Practical considerations for amplifier compensation").

It is good practice to adjust the sampling window backward to the last 50

TO ENSURE CONFI-DENCE, MAKE THE SAME MEASUREMENT WITH AN ALTERNA-**TIVE METHOD AND** SEE WHETHER RESULTS AGREE.

mV or so of amplifier slewing. This step allows you to observe the onset of ring time without encountering oscilloscope overdrive. The samplingbased approach provides this capability, and it is a powerful measurement tool. Slower amplifiers may require extended delay, sampling-window times, or both. You can use larger capacitor values in the delayed pulse-generator timing networks to meet these requirements.

#### **VERIFYING RESULTS**

The sampling-based settling-time circuit appears to be a useful measurement approach. A good way to ensure confidence is to make the same measurement with an alternative method and see whether results agree.

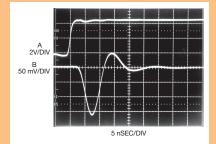

Classic sampling oscilloscopes are inherently immune to overdrive (Reference 8). You can use this feature and attempt a settling-time measurement directly at the clamped settle node (Figure 8). The circuit heavily overdrives a Tektronix type 661 with 4S1 vertical and 5T3 timing plug-ins, but the instrument is ostensibly immune to the insult (Figure 9). Trace A is the time-corrected input pulse, and

Figure 8 This alternative measurement method uses a 1-GHz Tektronix 661/4S1/5T3 sampling oscilloscope.

Trace B is the settle signal. Despite a brutal overdrive, the oscilloscope responds cleanly, giving a plausible settle signal.